Jasper Lake Fanless Showdown: ECS LIVA Z3 and ZOTAC ZBOX CI331 nano UCFF PCs Review

by Ganesh T S on July 8, 2022 8:30 AM EST- Posted in

- Systems

- ZOTAC

- Fanless

- ECS

- Passive Cooling

- UCFF

- Mini-PC

- Jasper Lake

Teardown and Thermal Design Analysis

Systems processed through our evaluation routine are first completely benchmarked prior to any teardowns. This ensures that we do not negatively impact any of the thermal solutions intended by the manufacturer. The details presented in this section were gathered after completing at least one benchmarking pass. However, the results of the evaluation (presented in later sections) needs significant thermal design context. Keeping that in mind, we opt to present the teardown and thermal design analysis ahead of the benchmark sections.

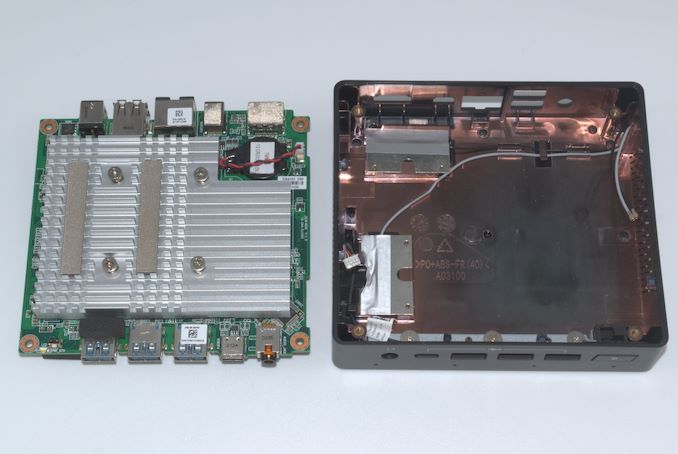

ECS LIVA Z3

The chassis of the ECS LIVA Z3 has a metal underside and a polycarbonate top. It is simple to disassemble - the underside is easily removed by taking out the four screws at the corners. This also needs to be done to get access to the SODIMM and M.2 2280 NVMe slots. The metal underside has a pre-mounted thermal pad to cool down any installed M.2 drive. There is also a small flap integrated on to the plate to allow for airflow.

The board has no additional mounting to the plastic top, and can be easily prised out by flexing the rear panel. Prior to that the DMICs connection to the board and the pigtail antennae connected to the M.2 WLAN card need to be disconnected.

The metallic glint on the underside of the top panel of the chassis above is highly misleading. The plastic top is completely covered and the only ventilation slots are on the sides. While the heat sink place on top of the board seems good enough to cool down a 6W TDP processor, the absence of ventilation slots on top appears strange at first glance. The closed nature makes convective cooling to draw the heat away from the thermal module challenging.

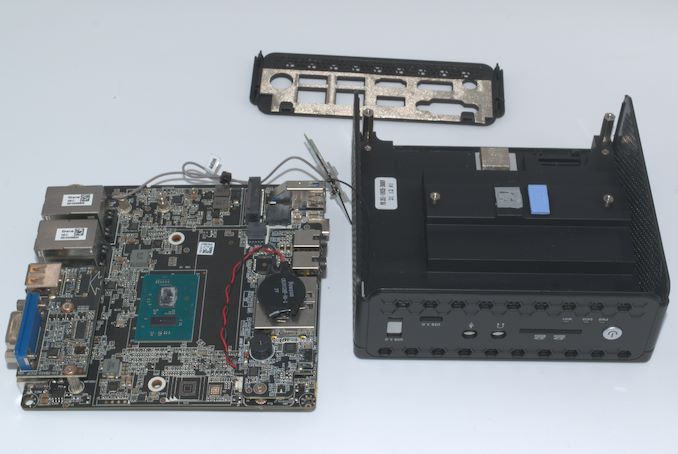

The Jasper Lake package can be seen bathed in thermal paste under the thermal module. Though Intel claims Jasper Lake to be a SoC (system-on-chip) in its documentation, we can see that it is technically a SiP (system-in-package) with two distinct dice - the processor and iGPU on top, and the Jasper Point PCH below it.

The first benchmarking pass results of the ECS LIVA Z3 were quite strange - often the system actually performed significantly worse than the ECS LIVA Z2 based on Gemini Lake. After suspecting thermal throttling due to the lack of convective cooling for the thermal module, we decided to repeat all the benchmarking for the bare board - i.e, with the top of the chassis removed and the DMICs / WLAN functionality discarded. The numbers for this configuration are referenced using ECS JSLM-MINI (the motherboard's model name) in the relevant sections.

ZOTAC ZBOX CI331 nano

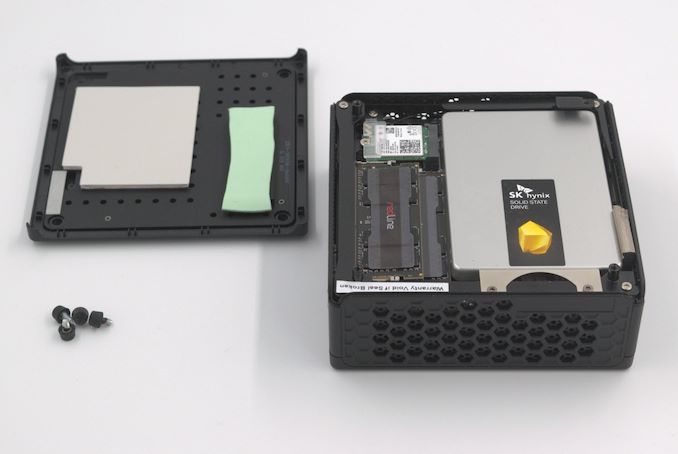

ZOTAC adopts a tool-less design, with the rubber feet doubling up as screws. They can be easily removed to access the underside of the board with the SODIMM slots and 2.5" SATA drive bay.

Further disassembly requires voiding the warranty by unscrewing the metal frame that holds the SATA caddy in place along with the motherboard standoffs. The standoffs themselves need to be removed using an uncommon screwdriver bit (thankfully, had it handy in the Mushkin Redline Screwdriver Toolkit).

The rear panel can then be snapped off (held by plastic tabs). The next step involves taking out the spring-loaded screws fastening the board to the heat sink, and this leads to a free board, as shown above.

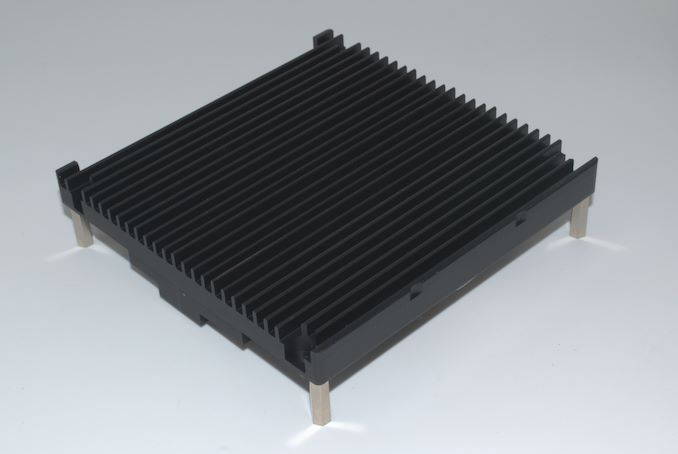

The heat sink is connected to the perforated plastic chassis using four small screws. which are straightforward to take out. The heat sink is quite heavy compared to the ECS LIVA Z3's thermal module. It has ridges right under the perforations - this allows increased area for heat dissipation, and the perforations allow for convective cooling.

Our main grouse with the thermal design of the ZBOX CI331 nano is the cooling support for the 2.5" drive. Typically, SATA drives do not get significantly hot. However, the underside of the ZBOX has almost no ventilation support. While a quantitative evaluation of the storage cooling mechanism is available in a later section, the problem in the hardware is brought out in the above picture. The green thermal pad attached to the raised block on the underside cools down the SODIMMs. The protection for the SATA drive is activated by affixing the thermal pad supplied in the package to the metal plate on the underside. However, it doesn't possess enough thickness and there is invariably an air gap between the top of the SATA drive surface and this pad. As a result, there is a bit of a compromise in the cooling for the 2.5" drive.

In the next section, we take a look at the system setup and follow it up with a detailed platform analysis.

52 Comments

View All Comments

ganeshts - Wednesday, July 13, 2022 - link

Are you aware of any boards / PCs with Elkhart Lake that supports in-band ECC? Vendors I talk to seem to indicate that there is some other feature X that gets disabled if you do in-band.. and that feature X is more important for their target market compared to in-band ECC. So, they do not enable in-band ECC in their products even if the processor supports it.mode_13h - Thursday, July 14, 2022 - link

> Are you aware of any boards / PCs with Elkhart Lake that supports in-band ECC?Sorry, I've not seriously investigated the matter.

> Vendors I talk to seem to indicate that there is some other feature X

> that gets disabled if you do in-band.

Wow. I'd love to know more! I figured the main tradeoff was just one of performance (and probably a less significant hit on memory capacity). I wonder why they don't just make it a user-configurable option.

TBH, I don't know specifics about how Intel implements it. I *assume* they simply set aside a chunk of physical address space to hold the ECC bits for the rest of the address space, but that's just a guess.

ganeshts - Tuesday, July 12, 2022 - link

Looks like you will leave me with nothing to write about for the Atlas Canyon review coming up later this week :)abufrejoval - Thursday, July 14, 2022 - link

If you keep me updated on the things in your pipeline, I'll make sure not to spoil things ;-)mode_13h - Thursday, July 14, 2022 - link

But I love your posts! I'll bet < 1% of the article readers look this deep into the comments.mode_13h - Wednesday, July 13, 2022 - link

Nice review!I had one of those ASRock Apollo Lake boards, but never got it to work. It's possible the RAM I got was incompatible, but it was decent quality (Crucial, IIRC) and their website claimed it worked with that board.

I was sad to see ASRock has no Jasper Lake-based successor, but TBH I'd rather have Elkhart Lake and its in-band ECC-support. I'm just now noticing that Asrock Industrial has some tasty looking options, there. Now, if I can just figure out where to buy a IMB-1003D...

abufrejoval - Thursday, July 14, 2022 - link

NUCs can take quite a while for the initial boot, even the Core based models.If I hadn’t been distracted at the time, I’d have already given up on the Jasper Lake NUC working with 64GB: I had been ready to turn it off by the time it showed the logo! Must have lasted something like 30 seconds or so, just to test and tune the RAM, which was DDR4-3200 after all and not quite the DDR4-2900 specs it officially prefers.

Actually, I really hate that vendors increasingly just program at most 2 settings into DIMMs these days, so you can’t recycle them on a different machine.

Once you realized that bits can rot, it’s very difficult to forego ECC. The very first IBM-PCs had parity and I’m not sure when it got dropped from mainline. Once I started running PCs as home servers, I’ve tried to make sure they had ECC memory. My workstations are also all 128GB ECC.

I bought the Atoms mostly to run QA for oVirt, not as a “production” platform: low cost and low power was key, ECC simply not an economically viable option.

They have been running non-stop for years now, with a collective 128GB of RAM and no glitch that I have ever noticed...

The first time I ever heard of inline ECC was in one of your posts here. After a short moment of “bug-eyed disbelief” it seemed to make sense in an era, when little ever happens in RAM below the granularity of a cache line: the days of truly random RAM where all accesses were equally …slow are long past us, I believe the original Compaq 386 was the first to exploit static column RAM.

I believe RAM compression was also implemented by an IBM server chipset many years ago, memory encryption is available on every modern laptop, so inline ECC seems very believable and not extremely costly: I’d just love to have the choice!

As a matter of fact, this gets me asking: Core chips seem to employ ECC practically everywhere on internal registers, caches and data paths, but do Atoms do likewise? I’d guess they would have to for the server variants, so leaving that out for the entry level chips seems almost extra effort, yet I can’t recall hearing any mention one way or another.

I’ve been trying to buy an Alder Lake replacement for a Haswell Xeon server with ASRocks IMB-X1712 mainboard mentioned here that supports DDR4-3200 ECC RAM. Unfortunately that’s another phantom product that never seems available for sale.

mode_13h - Thursday, July 14, 2022 - link

> Must have lasted something like 30 seconds or so, just to test and tune the RAMDoes the BIOS have an option to disable it, or at least a "fast boot" option?

> Once you realized that bits can rot, it’s very difficult to forego ECC.

The places where you really want ECC are those where a memory error can get persisted in data of non-trivial value. On fileservers and database servers, it's a must (unless the data is virtually disposable or they're simply providing read-only access).

In the worst case, a memory error can actually cause filesystem corruption. It's unlikely, but the thing to remember about memory errors is that they're not entirely random or isolated. A DRAM chip could conceivably fail in a way that suddenly results a large number of memory errors. This will usually crash the machine (if not using ECC), but you could plausibly suffer data corruption just before that happens.

> I bought the Atoms mostly to run QA for oVirt

My ASRock board was meant to replace my Raspberry Pi as a streaming media server, for in-home use.

> The first time I ever heard of inline ECC was in one of your posts here.

I'm pretty sure the first I'd heard of it was on here, as well. I had a similar reaction as yours, but the more I thought about it, the more sense it made. It'd be hard for me to prefer it when I could have the real deal, but not a bad compromise on something like an Atom-tier platform.

> little ever happens in RAM below the granularity of a cache line

Yeah, you could implement it by blocking off 1/8th of RAM (in truth, you'd only need 1/9th, but 1/8th would keep things aligned more nicely) and associating 8 bytes of ECC information per 64-bytes of physical address space. Depending how you implement it, the hit to memory bandwidth could be as little as 11%, for linear accesses.

TBH, I'm a little more mystified by the concept of memory compression. I guess it'd have to be block based, perhaps decompressing whole pages at a time? Then, when you page fault, some kind of index tells you where the page starts. There'd no doubt be some padding or unused space between the pages (or whatever granularity the blocks are). Perhaps the more interesting aspect would be deciding where to write newly-compressed pages.

Of the three, memory encryption seems the most straight-forward. You would likely have a 1:1 mapping, so the only tricky part is one of key management.

> Unfortunately that’s another phantom product that never seems available for sale.

I'll bet availability is being hampered by just a couple key components being extremely hard to source. I heard some motherboard vendors have been unable to source certain Ethernet MACs. Another example I've heard is RAID controllers.

abufrejoval - Thursday, July 14, 2022 - link

>> Must have lasted something like 30 seconds or so, just to test and tune the RAM>Does the BIOS have an option to disable it, or at least a "fast boot" option?

That was only ever an issue for the initial boot with that RAM. Once it has figured out the RAM speed settings any normal boot is at reasonable speeds.

I've research the Elkhart Lake Atoms a bit and they seem quite hard to find. Embedded systems with them sell for eye watering prices.

ZFS was always the typical example for why bit flips could have catastrophical consequences when you cache aggressively and keep key data structure in RAM for months or longer.

I use GlusterFS with VDO de-dup and compression on the Atoms, where a single bit flip could have similarly drastic consequences, but so far I've noticed no issue.

It seems that getting a low power ECC platform is intentionally made difficult, closest I've recently got was with Ryzen 5750G APUs, which isn't that low power nor that cheap.

DDR5 with real ECC seems even worse which is why the ASRock board with the W680 chipset and DDR4 support seems so attractive... and unavailable!

RAM compression: It definitely requires OS support, but other than that seems not too difficult to do. I saw a demo booth at the HiPEAC 2020 conference in Bologna from a Swedish startup I believe, that tries to sell the IP e.g. for integration in RISC-V.

mode_13h - Friday, July 15, 2022 - link

> Elkhart Lake Atoms a bit and they seem quite hard to find.They exist, if expensive and uncommon: https://www.newegg.com/p/1JW-003Z-00026

According to the manufacturer's site, it even seems to support in-band ECC:

https://www.mitacmct.com/IndustrialMotherboard=PD1...

However, that would seem to require the PD10EHI-X6413E model, which is *not* so readily available.

> ASRock board with the W680 chipset

Yeah, I was starting to browse for W680 boards, recently. I wish I could find an ATX (or micro-ATX) with 2x DDR5 slots, but every one I've found is either DDR4 or 4x DDR5 slots. Anyway, I'm not really in a hurry.

> RAM compression: ... seems not too difficult to do.

> ...a Swedish startup ... that tries to sell the IP

Okay, think about that for a second. Someone thought it offered enough value and is sufficiently hard that they started a company around it!