Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

by Dr. Ian Cutress on July 30, 2019 9:30 AM EST- Posted in

- CPUs

- Intel

- 10nm

- Microarchitecture

- Ice Lake

- Project Athena

- Sunny Cove

- Gen11

Combining 10nm CPU + 14nm Chipset

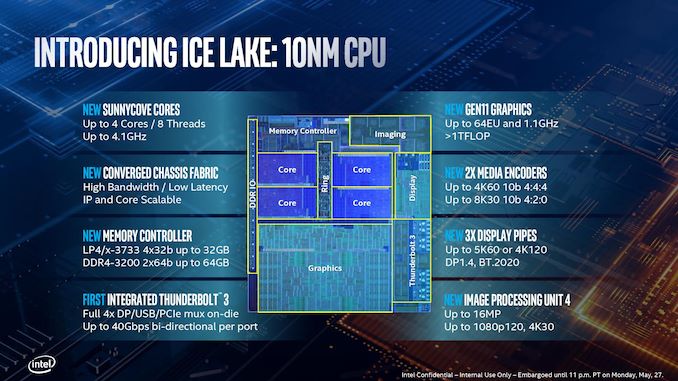

As with Intel’s previous low-power (sub 28W) mobile designs, the company will be combining the CPU and the chipset onto a single package. This typically helps in enabling a smaller motherboard design for thin and light systems that might want to dedicate that area to additional battery, or simply save the footprint altogether. The flip side is that there are more pin-outs, and the board design has to be suitable for the increased signal traces, but this is nothing new. For Ice Lake-U, Intel has stated that the CPU, which is being built on their second-generation 10nm "10+" process, will be paired with a new generation ‘14nm class’ chipset.

As stated on the previous page, the CPU will offer up to four cores, eight threads, go up to 4.1 GHz, provide integrated TB3 (more on that later), and a vast improvement to the graphics capabilities (also more on that later).

One of the big updates to the design will be enabling support for both DDR4 and LPDDR4/LPDDR4X on a single memory controller. Up until this point, only Intel’s latest Atom designs had LPDDR4 enabled, so this is a welcome addition to the main high-performance product line. In this instance Intel will support LPDDR4/X with up to four 32-bit channels at 3733 MT/s for 32 GB, or if a user needs more capacity, up to 64GB of DDR4-3200 with two 64-bit channels. The LPDDR4/X implementation will allow for lower idle power states, saving power and battery life when the memory is not in use, however it does this in exchange for maximum capacity. It’s an interesting tradeoff for sure. The peak power consumption of both modes in an equally populated system, given the respective frequency difference, should be similar.

One element that Intel hasn’t talked about is its ‘new converged chassis fabric’, which we believe to be a scalable power and environment control fabric that connects between chips in order to both transfer data but also to manage how and where power is applied within a system. The fact that Intel calls this ‘IP and Core scalable’ suggests that if vendors want to add additional supported chips to the system, say for example a future Intel AI chip, that might be possible and it could be controlled through this fabric. It will be interesting to see if Intel divulges any more of this information.

Not mentioned in this slide are the new performance enhancements, such as AVX-512 and other new instructions, which we’ll cover in detail a bit later.

The connection to the chipset is through a DMI 3.0 x4 link, as with current generations of Intel products.

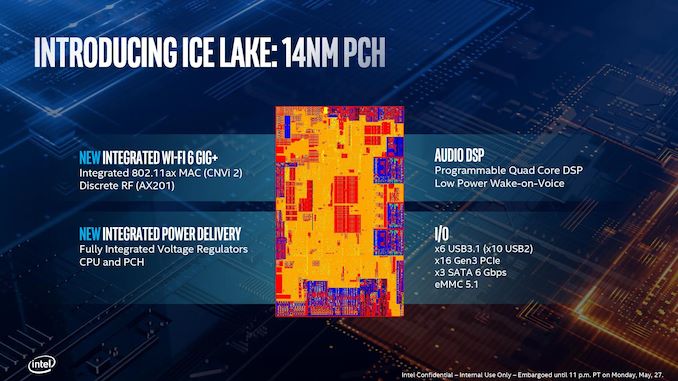

The new ‘14nm class’ chipset is also an update from Intel’s 8th Gen Core mobile processors. It does not yet have a series designation, but given the updates, this is likely to be a member of the 400-series chipset line.

With the new chipset, Intel has updated the proprietary CNVi protocol on the die to support CNVi 2, which is found on the latest Wi-Fi 6 Intel-Only RF modules, such as AX201. This update to a second generation implementation is likely to be for throughput reasons, given the increased bandwidth that Wi-Fi 6 provides over Wi-Fi 5.

Intel also promotes better integrated power delivery on the chipset, meaning that the PCH can share the same power rail as the CPU, reducing the number of on-board components inside the mobile system. This should reduce cost, and hopefully the thermal density of the power delivery onboard the chip doesn’t have a negative effect. Also on the power side, Intel states that the audio DSP on the chipset has also been improved for lower power operation.

On the IO side of the chipset, Ice Lake will support up to six ports of USB 3.1 (which is now USB 3.2 Gen 1 at 5 Gbps), or 10 USB 2.0 ports, or a mix. There are also 16 HSIO lanes which are broadly presented as PCIe 3.0, although given previous HSIO models it is likely that certain combinations of ports will be required for specific features. However this should afford at least two, if not three, potential PCIe 3.0 x4 NVMe drives in these systems. For SATA, there is access to three direct ports, but there is also an eMMC 5.1 link. Intel does not state if UFS is supported for super-small form factor systems.

Ice Lake is not Intel’s first crack at 10nm

We documented the history of Intel’s 10nm process with our review of the first 10nm CPU to come from the company. Our Core i3-8121U analysis of the Cannon Lake design is one Intel would rather forget – the manufacturing process didn’t yield, the frequency wasn’t there, the power consumption was too high, and the graphics were completely fused off. But hey, Intel still shipped it to customers by the end of 2017, and it found its way into some Chinese educational notebooks, and some NUCs, eventually, satisfying promises made to shareholders.

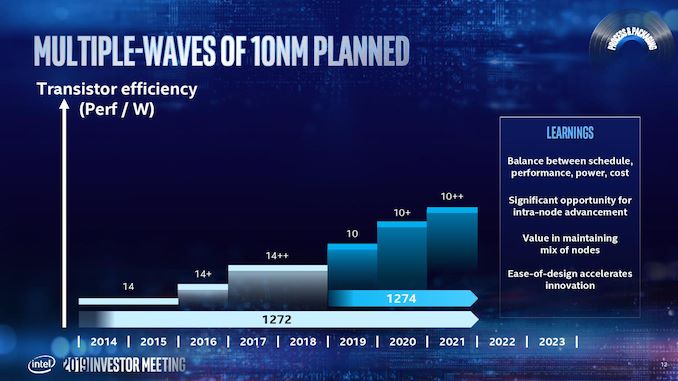

Fast forward almost 18 months, and we’re about to see Intel’s second take on 10nm with Ice Lake. Under Intel’s nomenclature, Ice Lake is technically being built with the ‘10+’ process, which is meant to be an improved version of the 10nm used in Cannon Lake. The fact that parts of the CPU are now working means that it earns that plus. Intel pointed to an extra metal layer (going from 12 to 13) in the manufacturing has helped with power delivery and frequency, and new transistor library designs and MIM caps have helped with voltages. Intel is also using a thin magnetic inductor array, and a recess in motherboard design for reduced package z-height.

As for Intel’s future, the company has stated at events that it is now developing future process nodes with these ‘BKM’ updates built into the lifecycle of the process node, such as 10+ and 10++ as part of the family of 10nm processes, and then beyond to 7nm with 7, 7+, and 7++ over the next few years. It’s worth noting that while Intel has officially shipped a first generation 10nm product, is promoting Ice Lake as a ‘10+’ second generation 10nm product, and has specified a number of 10nm class products up and down its product portfolio, we are still waiting on an official presentation about how Intel’s 10nm process works in a formal setting, rather than bits and pieces from events like ISSCC and IEDM. What we have pieced together from those events is likely out of date for 10+, however we do know that for 10nm Intel has three different libraries based on performance, each with different transistor densities: from 67 million transistors / mm2 for ultra-high performance, to 101 million transistors / mm2 for high-density logic. You can read more about it here.

107 Comments

View All Comments

repoman27 - Tuesday, July 30, 2019 - link

"It stands to reason then that the smaller package is for lower performance and low power options, despite being exactly the same silicon."I know the die floorplans are the same, but have Intel ever actually confirmed that U and Y (or H and S series for that matter) are the exact same silicon? Is it strictly binning and packaging that separates the platforms, or is there a slight tweak to the manufacturing process to target lower power / higher frequencies? Intel production roadmaps would seem to indicate this isn't just a binning situation, but I've never been entirely certain on that point.

And isn't Comet Lake-U 6+2 more likely to be 25 W, with Whiskey Lake-U 4+2 continuing to pull 15 W duty alongside Ice Lake-U 4+2?

CaedenV - Tuesday, July 30, 2019 - link

Those goals for Aethena are OK, but my old Dell XPS 12 with a carousel frame hit all of those except biometric, and wake from sleep in <1 sec... well, and the bezel... but that was due to the carousel design which I would LOVE to come back in a more modern form.Not saying these goals are bad... but if a 6 year old midrange laptop can hit almost all of them, then this isn't exactly aiming for something amazing.

AshlayW - Tuesday, July 30, 2019 - link

Quad core for 179 USD? What is this, 2015? No thanks.HStewart - Tuesday, July 30, 2019 - link

You do realize these are ultra-portable low power cpu's and not desktop chipsSamus - Tuesday, July 30, 2019 - link

Intel is a mess right now, the execution of this along with the naming scheme is ridiculous.shabby - Tuesday, July 30, 2019 - link

18% ipc gain and 20% clock lossPlace your bets how intel will spin this.

CHADBOGA - Tuesday, July 30, 2019 - link

I'm quite disappointed the issue of security mitigation in hardware was not addressed. o_OCityBlue - Saturday, August 3, 2019 - link

Disappointed, but not surprised.Security (and by inference the performance overhead required to implement proper security) is not important according to Anandtech/Ian Cutress. Which is obvious nonsense, so the only logical conclusion is that Anandtech are now a thoroughly biased outfit incapable of any critical reporting, which is quite sad particularly as it means all their articles (particularly when they relate to Intel) have to be read with a very heavy dose of cynicism.

eek2121 - Wednesday, July 31, 2019 - link

That picture of you biting a wafer is priceless.Santoval - Wednesday, July 31, 2019 - link

If Ice Lake-U has a ~3.5% higher single core performance (and, assuming the "multi-core overhead" is the same, multi-core performance as well) than Whiskey Lake-U despite having a 20% lower single core boost clock, then Sunny Cove must be an extremely impressive μarch. Or, er, that might not actually be the case : Ice Lake-U has a 18% higher IPC than the *original* Skylake of 2015, not Whiskey Lake. While Whiskey Lake is basically the same design it must have a somewhat higher IPC due to its much more mature process node and other optimizations.Let's be conservative and assume that Ice Lake-U (more specifically Sunny Cove) has a nice round 15% higher IPC than Whiskey Lake-U, with both at 15W. In that case, at a 20% lower boost clock Ice Lake-U should have a 5% lower performance than Whiskey Lake-U. Where is that +3.5% performance derived from then?

Even if we assumed that Ice Lake-U 18% IPC edge is over Whiskey Lake-U (highly unlikely, otherwise Intel would not have dug out the original Skylake from its computing grave) that would still translate to Ice Lake-U having a 1.5% lower single core performance than Whiskey Lake-U, rather than being 3.5% faster than it.

Maybe, just maybe, this is why Intel used just a single synthetic benchmark (surely compiled with aggressive flags and optimized for Intel CPUs) for that graph and avoided to disclose other synthetic benchmarks and real world use benchmarks? Is this also why they avoided to talk about CPU performance of Ice Lake in their Computex presentation, and instead focused on iGPU, Wifi and AI performance?

Based on the disclosed clocks and the "disclosed" (in obfuscated form) IPC of Ice Lake-U I just cannot see it being in any way faster than Whiskey Lake-U. It will probably also have worse power efficiency, since it has the same or higher TDP range at a much lower clock.