Intel’s Manufacturing Roadmap from 2019 to 2029: Back Porting, 7nm, 5nm, 3nm, 2nm, and 1.4 nm

by Dr. Ian Cutress on December 11, 2019 3:00 PM EST

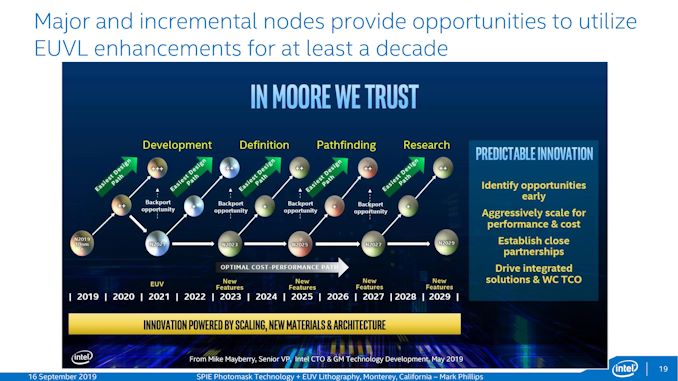

Update: After some emailing back and forth, we can confirm that the slide that Intel's partner ASML presented at the IEDM conference is actually an altered version of what Intel presented for the September 2019 source. ASML added animations to the slide such that the bottom row of dates correspond to specific nodes, however at the time we didn't spot these animations (neither did it seem did the rest of the press). It should be noted that the correlation that ASML made to exact node names isn't so much a stretch of the imagination to piece together, however it has been requested that we also add the original Intel slide to provide context to what Intel is saying compared to what was presented by ASML. Some of the wording in the article has changed to reflect this. Our analysis is still relevant.

One of the interesting disclosures here at the IEEE International Electron Devices Meeting (IEDM) has been around new and upcoming process node technologies. Almost every session so far this week has covered 7nm, 5nm, and 3nm processes (as the industry calls them). What we didn’t expect to see disclosed was an extended roadmap of Intel’s upcoming manufacturing processes. It should be noted that the slide presented at the conference by Intel's partner, ASML, was modified slightly from its original source.

They say a slide is worth 1000 words. Here’s 1000 words on Intel's future.

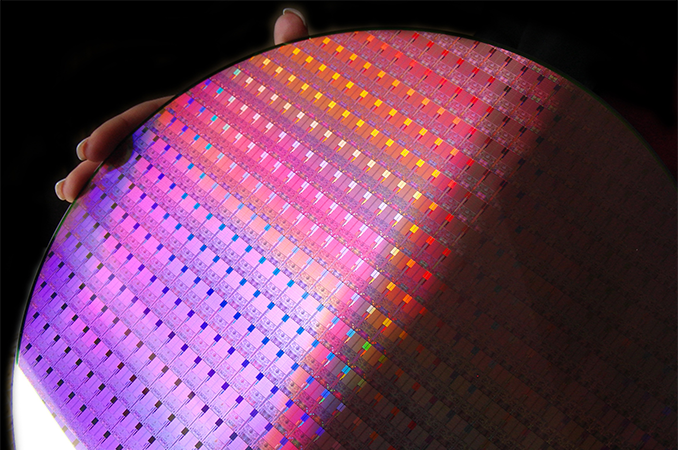

Intel's slide, as presented in September

This is Intel's original slide, not detailing which nodes in which years. However, it should be easy enough to figure out that each one of the elements in the bottom row is the next process node along, otherwise the +/++ wouldn't make sense.

ASML applied these assumptions to the slide it presented at the IEDM keynote, but the company did not disclose that they had modified the slide.

Intel's slide with ASML's animations overlayed, as shown in the slide deck distributed by ASML

So let’s go through some key areas.

1.4nm in 2029

Intel expects to be on 2 year cadence with its manufacturing process node technology, starting with 10nm in 2019 and moving to 7nm EUV in 2021, then a fundamental new node in each of 2023, 2025, 2027, 2029. This final node is what ASML has dubbed '1.4nm'. This is the first mention on 1.4nm in the context of Intel on any Intel-related slide. For context, if that 1.4nm is indicative of any actual feature, would be the equivalent of 12 silicon atoms across.

It is perhaps worth noting that some of the talks at this year’s IEDM features dimensions on the order of 0.3nm with what are called ‘2D self-assembly’ materials, so something this low isn’t unheard of, but it is unheard of in silicon. Obviously there are many issues going that small that Intel (and its partners) will have to overcome.

+, ++, and Back Porting

In between each process node, as Intel has stated before, there will be iterative + and ++ versions of each in order to extract performance from each process node. The only exception to this is 10nm, which is already on 10+, so we will see 10++ and 10+++ in 2020 and 2021 respectively. Intel believes they can do this on a yearly cadence, but also have overlapping teams to ensure that one full process node can overlap with another.

The interesting element to these slides is the mention of back porting. This is the ability for a chip to be designed with one process node in mind, but perhaps due to delays, can be remade on an older ‘++’ version of a process node in the same timeframe. Despite Intel stating that they are disaggregating chip design from process node technology, at some point there has to be a commitment to a process node in order to start the layouts in silicon. At that point the process node procedure is kind of locked, especially when it goes to mask creation.

In the slide, it shows that Intel is going to allow a workflow such that any first gen 7nm design could be back ported to 10+++, any first gen 5nm design could be back ported to 7++, and so on. One can argue that this roadmap might not be so strict with the dates – we have seen Intel’s 10nm take a long time to bake, so expecting the company to move with a yearly cadence on + updates alongside a two-year cadence with main process technology nodes would appear to be a very optimistic and aggressive cadence strategy.

Note that this isn’t the first mention of back porting hardware designs when it comes to Intel. With the current delays to Intel’s 10nm process technology, it has been widely rumoured that some of Intel’s future CPU microarchitecture designs, originally designed with 10nm (or 10+, 10++) in mind might actually find a home on a 14nm process due to the success of that process node.

Development and Research

Normally with process node developments, there will be different teams working on each process node. This slide states that Intel is currently in development of its 10+++ optimizations as well as the 7nm family. The idea is that the ‘+’ updates are capturing the low hanging fruit from a design standpoint every generation, and the number represents a full node benefit. Interestingly we see Intel’s 7nm being based on 10++, whereas in the future Intel sees 5nm come from the base 7nm design, and 3nm coming from 5nm. There is no doubt that some of the optimizations that enter each +/++ update will filter into future designs as and when they are needed.

In this slide, we have Intel’s 2023 node currently in the definition stage. At this IEDM conference there’s a lot of talk about 5nm in this timeframe, so some of those improvements (such as manufacturing, materials, consistency, etc.) will ultimately end up in Intel’s process depending on which design houses they partner with (historically Applied Materials). It is worth noting that 5nm is listed as a 2023 node, which is around the time that ASML will start selling its ‘High NA’ EUV machines to help with better path definition during the manufacturing process. I’m not sure if High NA will intercept at 5nm or 3nm, assuming this Intel roadmap has its dates correct and Intel is able to stick to it, but it is something to consider

Beyond 2023, Intel is currently in the ‘path-finding’ and 'research' mode. As always when looking this far out, Intel is considering new materials, new transistor designs, and such. At this IEDM conference we’re seeing a lot of talk of gate-all-around transistors, either as nano-sheets or nano-wires, so no doubt we’re going to see some of that as FinFET runs out of steam. TSMC is still using FinFETs for its 5nm process (Intel’s 7nm equivalent), so I wouldn’t be surprised if we see something like nano-sheets then nano-wires (or even hybrid designs) come into Intel’s manufacturing stack.

It’s worth also pointing out, based on the title of this slide, that Intel still believes in Moore’s Law. Just don’t ask how much it’ll cost.

138 Comments

View All Comments

Machinus - Wednesday, December 11, 2019 - link

Unless Intel ships 10nm processors in the next 3 weeks, this slide is just pure lies.nevcairiel - Wednesday, December 11, 2019 - link

10nm CPUs are already shipping in products on shelfes right now. But people don't like to accept the Ice Lake mobile systems, apparently.drothgery - Wednesday, December 11, 2019 - link

There's a bizarre thing on enthusiast web sites where many people seem to think desktops are the only important market segment for PC CPUs instead of the least reality where the only way you can argue they aren't the least important market segment is because of halo effects.Machinus - Friday, December 13, 2019 - link

It isn't bizarre at all. Those websites are correct. If you aren't selling desktop, hedt, and server processors on the same node as your competitors, it's because you failed in R&D and you can't produce them at all. You might be the last person on Earth who didn't know that AMD is having the biggest year in it's history, and it's not because of irrelevant laptop chips. Try reading a newspaper.nils_ - Thursday, December 12, 2019 - link

They also sold cannon lake products back in the day, though it was also mostly DOA. And there is no H Series Ice Lake for mobile workstations. Pretty limited product stack from my perspective.Santoval - Wednesday, December 11, 2019 - link

Let's do a naive and rough calculation of the projected transistor density of Intel's 1.4nm node.Intel's 10nm node has 100 million transistors per mm^2 (MTr/mm^2), which provides a nice round base for the calculation. Assuming Intel retains a doubling on average of transistors with each of their number nodes, their 7nm node will 200 MTr/mm^2, their 5nm node will have 400 MTr/mm^2 ... and finally their 1.4nm node will have 3.2 *billion* transistors per mm^2.

That is almost certainly physically impossible, so Intel might rather add +80% more transistors on average with each number node. That still means ~1.9 billion transistors per mm^2 at 1.4nm. A +70% extra transistors on average means ~1.4 billion transistors at 1.4nm. I have no idea if that is feasible, but Intel will probably be even less aggressive, maybe by adding +60% extra transistors on average until 2029 (or, much more likely, 2035), which would result in ~1 billion transistors per mm^2 at 1.4nm.

Even so, that would be the end of the road for transistors, unless new materials provide a speedup at lower densities.

Santoval - Wednesday, December 11, 2019 - link

p.s. My calculation employs as a base Intel's high performance 10nm node, which has the highest transistor density. That's the node with the ~100 MTr/mm^2. Intel has two other 10nm nodes though, one for moderate performance (moderate density) and one for lower performance/density. I cannot recall precise numbers but I think the moderate performance 10nm node (which, to my knowledge, is what Ice Lake-U/Y SoCs are fabbed on) has a density around 80 MTr/mm^2 and the lower density 10nm node has 55 to 60 MTr/mm^2.I did not take into account these other two nodes because the calculation would become quite more complex. Intel's high density 10nm node is intended for -H & -S desktop CPUs (which do not exist and apparently will not exist in the entire 2020 either, due to poor yields) and Xeon CPUs.

Llawehtdliub - Wednesday, December 11, 2019 - link

Intel shareholders in this comment section.Just sell boys. Their stock is going to take a big hit Q1 2020.

bananaforscale - Wednesday, December 11, 2019 - link

Given the 14nm+++++++++++++++ mess I'm not holding my breath wrt that timeline being accurate.shabby - Wednesday, December 11, 2019 - link

Is it April fools already?