MIPS Technologies Updates Processor IP Lineup with Aptiv Series

by Ganesh T S on May 10, 2012 8:55 AM ESTThe interAptiv family brings multithreading to the table, something which ARM hasn't started implementing yet. As our Lava Xolo smartphone revealed, implementing simultaneous multi-threading is highly beneficial for performance, particularly in current day workloads.

MIPS claims that 3 interAptiv cores deliver performance similar to / slightly exceeding what could be obtained from 2x Cortex-A9 / 3x Cortex-A5 cores with the same silicon area. Of course, CoreMark numbers heavily favor the interAptiv cores.

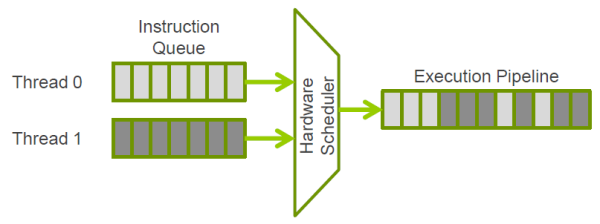

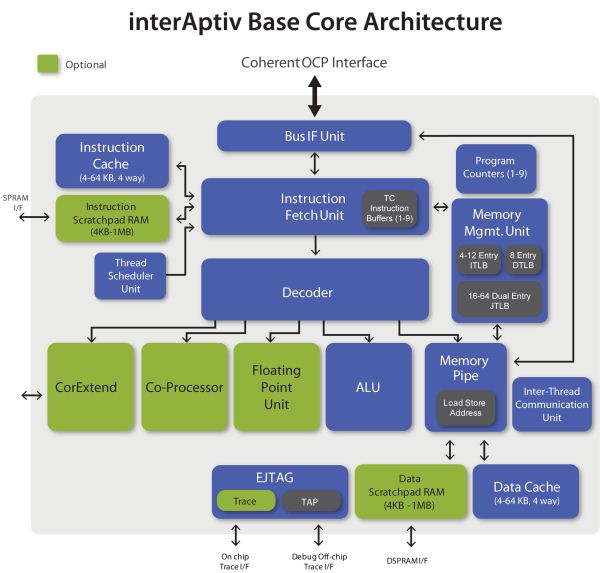

In the interAptiv family, the CPU execution pipeline is shared by multiple threads, which allows the mitigation of the performance impact of memory access latencies. Since interAptiv is targeted towards real time workloads, a hardware scheduler enables a better QoS.

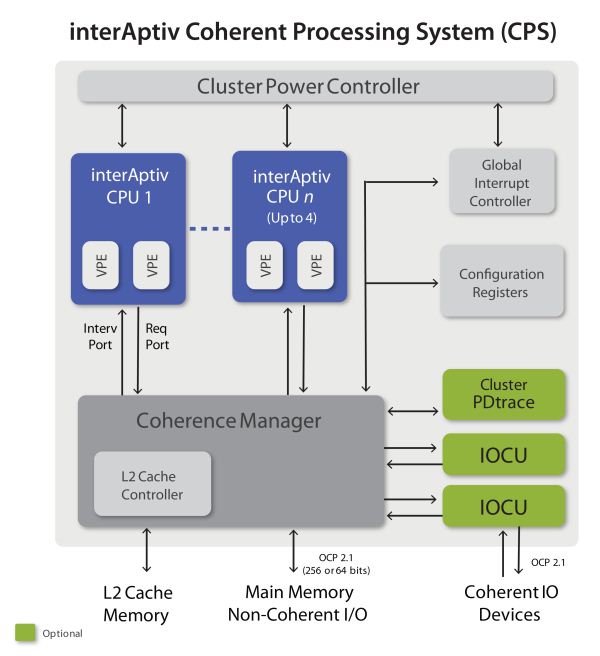

MIPS terms the threads as VPEs (virtual processing elements). The pipeline itself is 9 stages long and is in-order. An optional multi-threaded IEEE 754 FPU can be added if necessary. DSP ASE is available, as is EVA (similar to the proAptiv family). The CPS used with the multi-core interAptiv family has the same features as that used by the proAptiv.

Compared to the proAptiv, the interAptiv core architecture allows for core clock shutdown during outstanding bus requests, intelligent way selection in the L1 instruction cache and 32-bit L1 data cache access as options for power reduction. [ Update: Intelligent way selection in the L1 instruction cache is also available in the proAptiv family ]

In the TSMC 40nm G process, the interAptiv family members can run at up to 1 GHz for applications involving multi-threading with QoS and at up to 1.2 GHz for multi-threading without QoS. If DSP ASE is not desired, implementations can run at up to 1.5 GHz for networking applications. [ Update: The quoted frequency numbers are 'sweet spots' in terms of power consumption and other application specific requirements. As mentioned in the previous section, the frequency of operation can be scaled depending on customer requirements and is not related to the presence of absence of DSP ASE / QoS ]

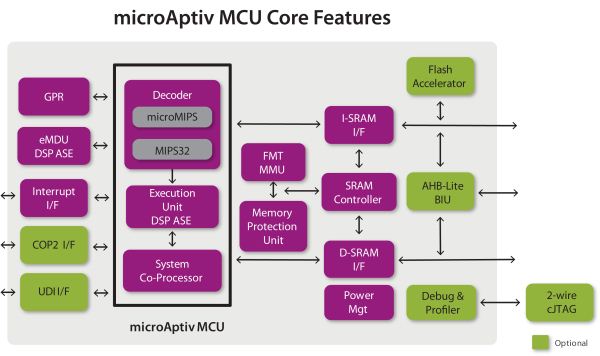

The microAptiv architecture is a superset of the M14K/c cores with microMIPS code compression support. With integrated DSP ASE, signal processing comes in at a lower cost. There are options to implement without caches / MMUs depending on the application.

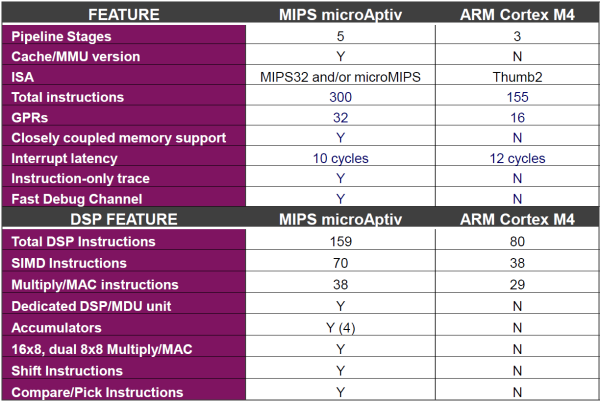

This 5 stage pipeline architecture can run at up to 400 MHz in a 65nm LP process. MIPS also presented a side-by-side comparison of the Cortex-M4 and the microAptiv family:

Obviously, the extra features don't come without an area penalty. In a 90nm LP process, Cortex-M4 has a floorplanned area of 0.17 mm2 compared to the 0.42 mm2 of the microAptiv MCU (cacheless version). [ Update: MIPS claims that the area numbers are not apples-to-apples comparison. Under similar implementation conditions in 90LP - read, area optimized - MIPS expects the microAptiv family to have only 0.01 mm2 extra area. Our data is from ARM's Cortex-M4 specifications. We agree it is difficult to compare the area requirements, but readers should note that there is no free lunch when it comes to feature set vs. die area ]

40 Comments

View All Comments

CrankUpThePowerIgor - Thursday, May 10, 2012 - link

We have 32 bit cores?Phones need 64 bit as much as they need 4 cores, but I'm sure it would sell ;)

jjj - Thursday, May 10, 2012 - link

You keep mentioning die area but never list some actual numbers (or maybe i missed those?). Die are wise it is amusing that they only compare to A15 .Since it seems that it can't clock as high as A15 it's not a fair comparison.The 2 don't target the same markets anyway so w/e.The lower clocked core(s) solution sounds way too much like Nvidia's 4+1 ,wonder if they'll have anything to say about that.

"it looks likely that the architecture of choice in the mobile / tablet space will become a two way shootout between ARM and x86"

Unless China decides to go with it's own ISA and then things will get a bit more complicated.

bji - Thursday, May 10, 2012 - link

That is a terrible marketing name.bji - Thursday, May 10, 2012 - link

Am I really reading that right? Are those memory controllers really that small? Sounds barely visible to the naked eye.ganeshts - Thursday, May 10, 2012 - link

Yes, they are really small. Usually, there are some peripherals around them on the die, and then, there is the packaging which makes it visible to the eye :)metafor - Thursday, May 10, 2012 - link

It should be noted that Krait is on the 28LP node currently and that corresponds to its frequency of 1.5GHz. ARM's A15 numbers on 28LP are around ~2GHz (OMAP 5430 being the primary example).ganeshts - Thursday, May 10, 2012 - link

We can't have too many inferences from the frequency of operation.With appropriate choice of libraries, usage of low Vt cells etc., Qualcomm could have probably gotten Krait to run at 2 GHz had they wished. It probably means that Qualcomm is satisfied with 1.5 GHz for their target market. ARM's A15 numbers will vary widely, and the OMAP 5430 is just one case..

We should actually compare operating frequency with the same set of libraries / same process node / same operating corner, but different vendors quote different circumstances.. So, it is not easy to make an apples-to-apples comparison.

Daniel Egger - Thursday, May 10, 2012 - link

I'm really not sure you're all getting the point here with all the ARM comparison. MIPS is not even trying (at least not hard) to get into the smartphone game. MIPS is a really strong player in the consumer grade network equipment market -- think WLAN APs and routers, DSL Modems, Mifis, etc.. There's almost no ARM or x86 anywhere to be found but since networking speeds are ever increasing an architecture update is sorely needed!You can compare MIPS and ARM and x86 (and if you're serious about it you'd also include Freescale) as much as you'd like but the matter of fact is: Each of these architecture has at least one weak spot that disqualifies it for some market segments:

- Most ARM based processors have lousy I/O possibilities (crappy or no network, no PCIe)

- Most MIPS implementations do not have powerful GPUs and CPU performance is not the best

- x86 needs too many external components and it is effectively only available from one vendor and non-synthesizable

- Freescale (PPC) implementations also do not have powerful GPUs, are too power hungry and far too expensive for most uses

ganeshts - Thursday, May 10, 2012 - link

Oh! MIPS is definitely trying to get a toehold in the smartphone market. In fact, I looked at a few of their smartphones in their HQ (all being sold in China).The drawbacks you indicate are not a problem with the processor IP. Rather, it is the SoC vendor's choice on what peripheral IPs are integrated along with the processor.

Penti - Thursday, May 10, 2012 - link

Naw they are not really trying, the Ingenic chip the Chinese devices uses is a custom design by the Chinese firm Ingenic. Not CPUs designed by MIPS Technologies. Those has to compete with Chinese as well as cheap semi-local Taiwanese ARM-designs with ARM RTL-cores and embedded baseband too. Nothing much happening there. Not from Mips Tech standpoint any way. The MIPS SoCs can use the same third party synthesizeable IP GPUs, video engines as the ARM counterparts and so on. But don't expect much in the form of baseband modems on MIPS processors. Smartphones run fine with either x86, ARM or MIPS though. Android has support for them all. A few years ago there were some other architectures involved in the business too. Let's see if anybody uses MIPS Technologies IP cores to build phones first before shouting anything. We won't really have the same situation if you can't use RTL-cores at any fab and multiple vendors delivering solutions on that. It's hard to compete if there is just one vendor with their own custom designs. Freescale will continue their i.MX ARM line for phones/tablets. ARM is taking over the whole CE field including TVs, blu-ray players and so on too for that matter. Still some good MIPS-designs around though. But there are good designs of most stuff around. Tools and software certainly would draw you to ARM though.