Cadence & Micron DDR5 Update: 16 Gb Chips on Track for 2019

by Anton Shilov on October 17, 2018 10:15 AM EST

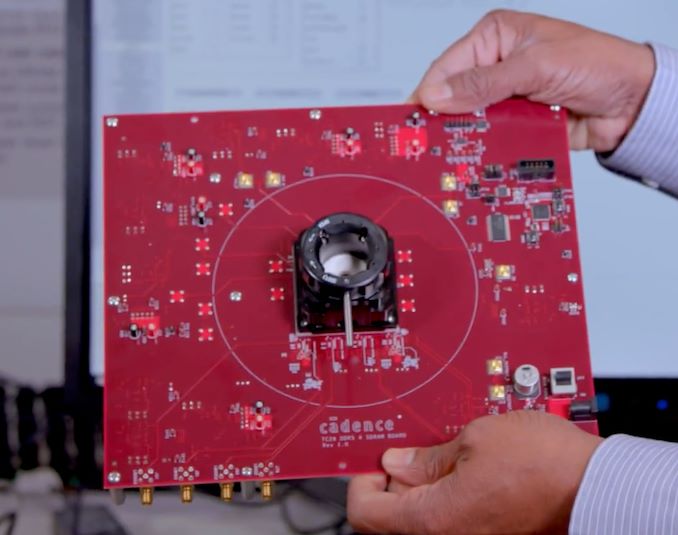

Earlier this year Cadence and Micron performed the industry’s first public demonstration of next-generation DDR5 memory. At a TSMC event earlier this month the two companies provided some updates concerning development of the new memory technology. As it appears, the spec has not been finalized at JEDEC yet, but Micron still expects to start production of DDR5 memory chips in late 2019.

As noted back in May, the primary feature of DDR5 SDRAM is capacity of chips, not just a higher performance and a lower power consumption. DDR5 is expected to bring in I/O speeds of 4266 to 6400 MT/s, with a supply voltage drop to 1.1 V and an allowable fluctuation range of 3% (i.e., at ±0.033V). It is also expected to use two independent 32/40-bit channels per module (without/or with ECC). Furthermore, DDR5 will have an improved command bus efficiency (because the channels will have their own 7-bit Address (Add)/Command (Cmd) buses), better refresh schemes, and an increased bank group for additional performance. In fact, Cadence goes as far as saying that improved functionality of DDR5 will enable a 36% higher real-world bandwidth when compared to DDR4 even at 3200 MT/s (this claim will have to be put to a test) and once 4800 MT/s speed kicks in, the actual bandwidth will be 87% higher when compared to DDR4-3200. In the meantime, one of the most important features of DDR5 will be monolithic chip density beyond 16 Gb.

Leading DRAM makers already have monolithic DDR4 chips featuring a 16 Gb capacity, but those devices cannot offer extreme clocks or I/O speeds because of laws of physics. Therefore, companies like Micron have a lot of work to do in a bid to bring together high DRAM densities and performance in the DDR5 era. In particular, Micron is concerned about variable retention time, and other atomic level occurrences, once production technologies used for DRAM reach 10 – 12 nm. Meanwhile, the DDR5 Add/Cmd bus already features on-die termination to make signals cleaner and to improve stability at high data rates. Furthermore, high-end DDR5 DIMMs will have their own voltage regulators and PMICs. Long story short, while the DDR5 standard is tailored to wed performance and densities, there is still a lot of magic to be done by DRAM manufacturers.

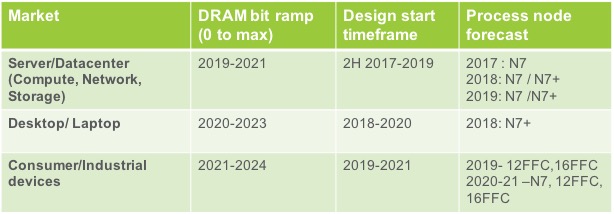

Micron expects to start production of 16 Gb DDR5 chips using its “sub-18nm” fabrication process late in 2019, though this does not necessarily mean that actual applications featuring this memory will be available by the end of next year. Cadence already has DDR5 IP (controller + PHY) implemented using TSMC’s N7 (7 nm DUV) and N7+ (7 nm DUV+EUV) process technologies, so chip developers have what they need to design SoCs compatible with the new type of memory. Cadence is working on DDR5 IP for more advanced process technologies.

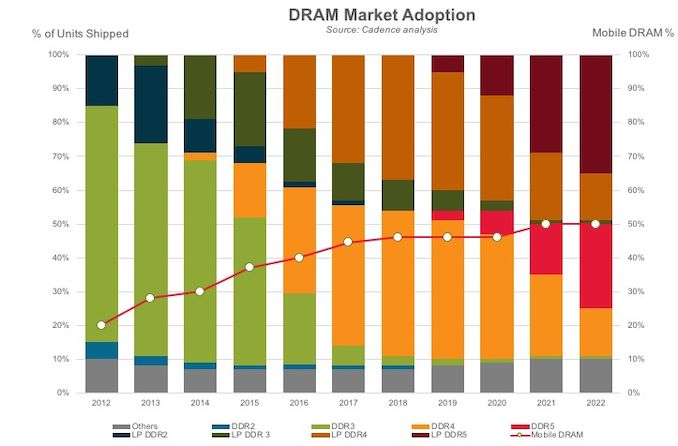

Given the key advantages of DDR5, it is not surprising that Cadence forecasts servers to be the first applications to use the new type of DRAM. What is particularly interesting is that Cadence believes that client SoCs made using N7+ process will support DDR5, which essentially means chips due to hit the market in 2020. Given rather quick ramp of DDR5 production predicted by Cadence, it looks like the new DRAM will be supported by a wide range of chips.

Related Reading:

- Cadence and Micron Demo DDR5-4400 IMC and Memory, Due in 2019

- JEDEC: DDR5 to Double Bandwidth Over DDR4, NVDIMM-P Specification Due Next Year

- Micron, Rambus, & Others Team Up To Spur GDDR6 Adoption in Non-GPU Products

- Samsung Updates on GDDR6 Portfolio: 8 Gb and 16 Gb at Multiple Speeds

- Samsung Starts Mass Production of 16Gb GDDR6 Memory ICs with 18 Gbps I/O Speed

- GDDR5X Standard Finalized by JEDEC: New Graphics Memory up to 14 Gbps

- JEDEC Publishes HBM2 Specification as Samsung Begins Mass Production of Chips

Source: Cadence

18 Comments

View All Comments

The Chill Blueberry - Wednesday, October 17, 2018 - link

Hoping the bandwidth improvements doesn't come with a big latency increase.JoeyJoJo123 - Wednesday, October 17, 2018 - link

They will. DDR5 is more focused on increasing capacity and lowering voltage (ie: increased efficiency), with the drawback of slightly higher overall latency (despite running at higher MT/s). Primarily designed due to servers requiring more and more memory, and these are the end devices for DRAM that end up both consuming the most wattage and where the most revenue is made.From a business standpoint, yeah, it makes sense that they'd focus the design to benefit that market the most.

From a consumer standpoint, yeah, it's dumb that we're going to lose a bit of latency, but at the end of the day this should mean DRAM is cheaper to produce for the same capacity (and DRAM pricing is the biggest problem on the market for consumers right now), and if latency's that big a deal to you, G.Skill/Crucial/Corsair/etc. will be providing memory kits that can overclock to higher MT/s and lower latencies than official JEDEC specs for DDR5.

Ian Cutress - Wednesday, October 17, 2018 - link

CAS Latency goes up, sure, but when bundled with the frequency gain, the real world latency often stays around the same. We're still a long way out from the fine tuning that will be required when the IP actually goes into real world chips.JoeyJoJo123 - Wednesday, October 17, 2018 - link

I'm aware, I was speaking of CAS Latency and other individual RAM subtimings, as you presumed correctly.Total latency does stay roughly the same generation to generation as you've stated, although I expect this generation to dip just a bit in total latency, though, because I don't particularly see any kind of "Moore's law equivalence" (in regards to a presumed law that every generation of DRAM always increases MT/s, increases capacity, slows subtimings, but still maintains the same total latency) to hold up over time for memory.

I'd like to be wrong, but the thing is DDR4 was ~supposed~ to bring cost and capacity benefits over DDR3. That didn't pan out. At this point I don't think DRAM can achieve improving all three of the following:

1) capacity

2) cost

3) speed

DDR4 failed on cost over DDR3, and the speed stayed the same. We just got 1 improvement with capacity, kept the speed the same, and got worse cost. So I don't even think we'd be looking at a "pick 2 of 3" scenario for the above, but maybe just improve 1, keep the other constant, and the other gets worse. And my bet is on improving capacity, keeping the current (exorbitant) memory cost, and slightly worse speed.

That being said, these are obviously all my own speculation given trends I've personally noticed in the memory market over time. My speculation is just that-- speculation.

Mr Perfect - Wednesday, October 17, 2018 - link

Keep in mind that the DRAM manufacturers have been engaging in price fixing with DDR4. https://www.theregister.co.uk/2018/04/30/dram_vend...DDR5 may suffer the same fate.

JoeyJoJo123 - Wednesday, October 17, 2018 - link

Possible, but they're currently under supervision/investigation of collusion. Also, current projected DRAM prices are expected to lower into Q4, although after that memory prices are expected to rise again.James5mith - Thursday, October 18, 2018 - link

Lower to what? 2016 era prices? I bought the same set of 32GB (2x16GB) DDR4-2666 SO-DIMMs three times (two NUCs and a laptop).2016 - $171 for the kit

2017 - $239 for the kit

2018 - $370 for the kit

Adramtech - Thursday, October 18, 2018 - link

"Keep in mind that the DRAM manufacturers have been engaging in price fixing with DDR4." That lawsuit is pretty flimsy, having read it in its entirety.James5mith - Thursday, October 18, 2018 - link

DRAM pricing is only a problem due to price fixing by the major manufacturers. We are just about due for another lawsuit.Prices have double since 2016, not held stable, not slightly fluctuated. Doubled. There was not a magic cause for the price of the same thing you made two years ago being twice as expensive now. That's pure greed, and sadly with hyperscale companies consuming the lion's share of the product, they've been able to get away with it.

brunis.dk - Wednesday, October 17, 2018 - link

I dont know why everyone keeps raving on about latency for memory, with all the level2 and level3 caches on CPU's it's a like fraction of a nice market where memory latency makes a difference. It's been tested over and over .. why do people waste money on these DDR4->9999 MEGAHURTS, when they could get a faster cpu or gpu and actually increase framerate?