European Processor Initiative Backed SiPearl Announces Licensing of Arm Zeus Neoverse CPU IP

by Andrei Frumusanu on April 21, 2020 12:00 PM EST

SiPearl, a new France-based company that is being backed and receiving grants from the European Comission’s European Processor Initiative project, has announced that is has licensed Arm’s next-generation Neoverse processor, codename Zeus.

SiPearl is still in its infancy as it’s only been founded in January of this year, but the new company has lofty goals as it aims to be the design house for Europe’s HPC goals.

Maisons-Laffitte, France, 21 April 2020 – SiPearl, the company that is designing the high-performance, low-power microprocessor for the European exascale supercomputer, has signed a major technological licensing agreement with Arm, the global semiconductor IP provider. The agreement will enable SiPearl to benefit from the high-performance, secure, and scalable next-generation Arm® Neoverse™ platform, codenamed ‶Zeusʺ, as well as leverage the robust software and hardware Arm ecosystem.

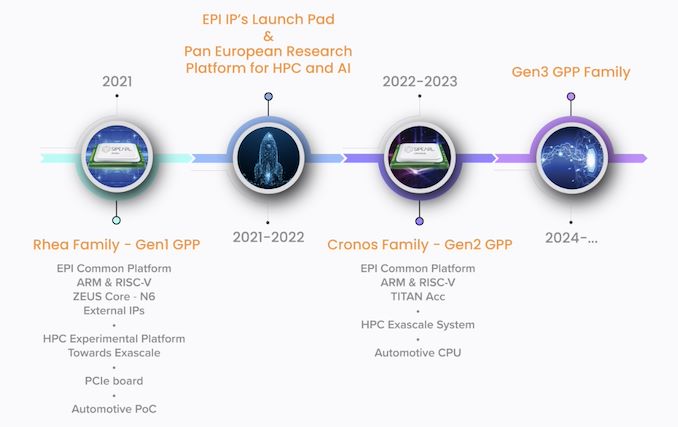

Taking advantage of the Arm “Zeus” platform, including Arm’s POP™ IP, on advanced FinFET2 technology enables SiPearl to accelerate its design and ensure outstanding reliability for a very highend offering, in terms of both computing power and energy efficiency, and be ready to launch its first generation of microprocessors in 2022.

The announcement today more specifically covers the company’s licensing deal with Arm – pronouncing that they will be using the new “Zeus” core. Zeus follows up on the Neoverse N1 core “Ares”, and should be the infrastructure sibling to Arm’s Cortex-A77 mobile cores.

On the EPI website, the EC also details a roadmap of the project, with the detail of “N6” alongside the Zeus core description, which likely means the chip will be designed on TSMC’s N6 process node – an improved and evolved variant of the manufacturers N7 node which retains design compatibility.

The project is another boost to the Arm server ecosystem after the latest success of Amazon’s Graviton2 chip as well as Ampere’s announcement of the Altra platform which we’ll be seeing in a few months’ time.

Related Reading:

- Arm Announces Neoverse N1 & E1 Platforms & CPUs: Enabling A Huge Jump In Infrastructure Performance

- Arm Announces Neoverse Infrastructure IP Branding & Future Roadmap

- Amazon's Arm-based Graviton2 Against AMD and Intel: Comparing Cloud Compute

- Next Generation Arm Server: Ampere’s Altra 80-core N1 SoC for Hyperscalers against Rome and Xeon

- 80-Core N1 Next-Gen Ampere, ‘QuickSilver’: The Anti-Graviton2

10 Comments

View All Comments

defaultluser - Tuesday, April 21, 2020 - link

So much for Risc-V in Supercomputing. I imagine they could build their own vector unit, with the new customized ARM instructions.SarahKerrigan - Tuesday, April 21, 2020 - link

EPI will be using an ARM+SVE host and a custom RISC-V accelerator. (I'm not particularly convinced this configuration makes sense, but them's the breaks.)TeXWiller - Wednesday, April 22, 2020 - link

They want to develop a EU based processor IP that isn't subject to the future economic instabilities caused by political and nationalistic fervors. The purists even have wanted to ditch ARM after Brexit but that would not be practical approach at this point. The EPI targets also the embedded world so the purists, or "pan-EU nationalists" (ducks, covers and suchs..=)) will eventually get what they desire.The SVE allows 2k vector lengths, so there shouldn't be a density argument for a while, but there could be the argument for interconnects and modularity that doesn't fit in the wider ARM ecosystem, or that of programmability. The Spanish have already been pushing out prototypes on the subject.

halcyon - Friday, April 24, 2020 - link

Makes sense.The world is diving into USA vs China - and both spy/steal/try to block each other.

Makes sense for Europe to roll their own and get some independence.

It'll take years, if not decades, hopefully EU/Europe sticks with it.

More competition will be better.

mode_13h - Tuesday, April 21, 2020 - link

If you look at the slide, it says "EPI Common Platform ARM & RISC-V" under both Gen1 GPP and Gen2 GPP. I don't want to read too much into that, but don't count out RISC-V just yet.ksec - Wednesday, April 22, 2020 - link

> So much for Risc-V in Supercomputing. IThat is only enthusiast thinking. No vendor in SuperComputing ever thought about doing it seriously. ( Other than for Press or Media Coverage )

Using RSIC-V for GPGPU is a different story.

abufrejoval - Wednesday, April 22, 2020 - link

While the chip will have ARM tiles, that's mostly for the mainstream code, data preparation, orchestration etc. where RISC-V isn't competitive today.For the HPC support it's very wide RISC-V vector units and specialized tiles with FPGA and Kalray units.

The fun part about the RISC-V vector units is that the code can run unchanged (=without even a recompile) on vectors of very different lengths, something other SIMD ISAs can't.

I've seen demos of the compiler work that the Barcelona Supercomputing Center does at HiPEAC in Bologna in January.

They promise a PCIe board for developers... soonest!

Wilco1 - Wednesday, April 22, 2020 - link

You mean RISC-V has copied the vector length idea already used in Arm's SVE?About 80% of the first generation will be Zeus, the rest split between 3 different accelerators, see eg. https://www.nextplatform.com/2019/06/10/europes-ho...

It will be interesting to see how it does, but given this and Zeus being a high-end core, it's likely most of the achieved FLOPS are from Arm's SVE.

mode_13h - Friday, April 24, 2020 - link

I like how people are just pretending that Xeon Phi didn't happen. Knights Landing had 2x 512-bit vector units per core. Even if it'd had wider, it still wouldn't have been competitive with real GPUs.GPUs aren't just a general-purpose ISA with wide vector units. Intel learned that the hard way.

sunshinerevans55 - Sunday, May 3, 2020 - link

I basically make about $12,000-$18,000 a month online. It’s enough to comfortably replace my I was amazed how easy it was after I tried it . This is what I’ve been doing old jobs income, especially considering I only work about 10-13 hours a week from home… www.iⅭash68.Ⅽom